Peneliti MIT telah mengembangkan metode fabrikasi baru yang memungkinkan produksi perangkat elektronik yang lebih hemat energi dengan menumpuk beberapa komponen fungsional di atas satu sirkuit yang ada.

Di sirkuit tradisional, perangkat logika yang melakukan komputasi, seperti transistor, dan perangkat memori yang menyimpan data dibangun sebagai komponen terpisah, sehingga memaksa data berjalan bolak-balik di antara keduanya, sehingga membuang-buang energi.

Platform integrasi elektronik baru ini memungkinkan para ilmuwan membuat transistor dan perangkat memori dalam satu tumpukan kompak pada chip semikonduktor. Hal ini menghilangkan banyak energi yang terbuang sekaligus meningkatkan kecepatan komputasi.

Kunci dari kemajuan ini adalah material baru yang dikembangkan dengan sifat unik dan pendekatan fabrikasi yang lebih presisi sehingga mengurangi jumlah cacat pada material. Hal ini memungkinkan para peneliti untuk membuat transistor yang sangat kecil dengan memori internal yang dapat bekerja lebih cepat daripada perangkat canggih sekaligus mengonsumsi lebih sedikit listrik dibandingkan transistor serupa.

Dengan meningkatkan efisiensi energi perangkat elektronik, pendekatan baru ini dapat membantu mengurangi peningkatan konsumsi listrik dalam komputasi, terutama untuk aplikasi yang menuntut seperti AI generatif, pembelajaran mendalam, dan tugas-tugas visi komputer.

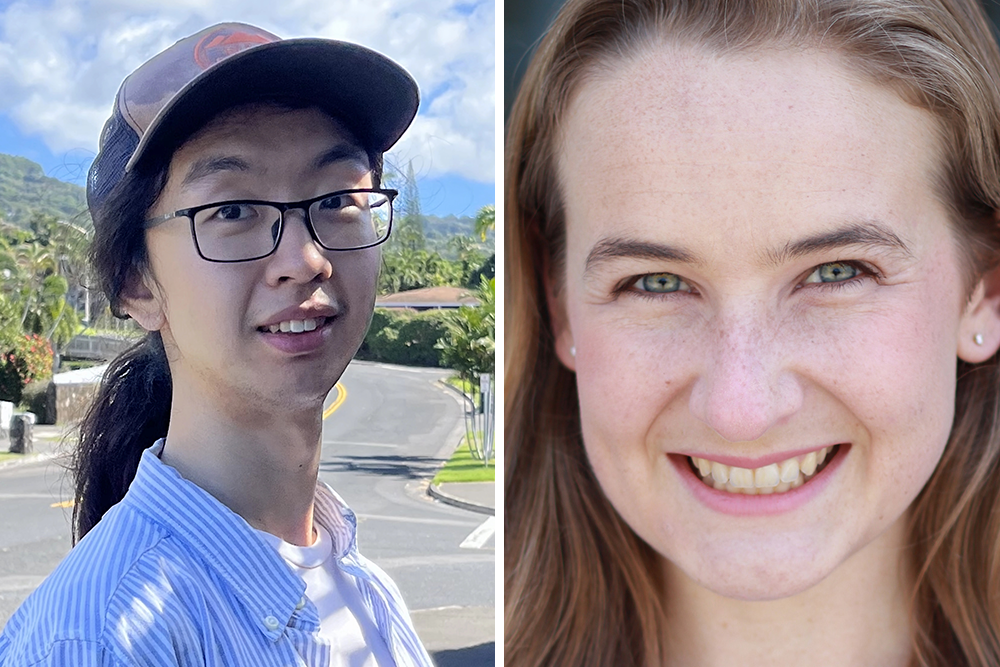

“Kita harus meminimalkan jumlah energi yang kita gunakan untuk AI dan komputasi data-sentris lainnya di masa depan karena hal ini tidak berkelanjutan. Kita memerlukan teknologi baru seperti platform integrasi ini untuk melanjutkan kemajuan tersebut,” kata Yanjie Shao, seorang postdoc MIT dan penulis utama dua makalah tentang transistor baru ini.

Teknik baru ini dijelaskan dalam dua makalah (satu diundang) yang dipresentasikan pada Pertemuan Perangkat Elektron Internasional IEEE. Shao bergabung dalam makalahnya dengan penulis senior Jesús del Alamo, Profesor Teknik Donner di Departemen Teknik Elektro dan Ilmu Komputer (EECS) MIT; Dimitri Antoniadis, Profesor Teknik Elektro dan Ilmu Komputer Ray dan Maria Stata di MIT; serta lainnya di MIT, Universitas Waterloo, dan Samsung Electronics.

Membalikkan masalah

Chip CMOS (semikonduktor oksida logam komplementer) standar biasanya memiliki ujung depan, tempat komponen aktif seperti transistor dan kapasitor dibuat, dan ujung belakang yang mencakup kabel yang disebut interkoneksi dan ikatan logam lain yang menghubungkan komponen chip.

Namun sebagian energi hilang saat data berpindah antar ikatan ini, dan sedikit ketidakselarasan dapat menghambat kinerja. Menumpuk komponen aktif akan mengurangi jarak yang harus ditempuh data dan meningkatkan efisiensi energi chip.

Biasanya, sulit untuk menumpuk transistor silikon pada chip CMOS karena suhu tinggi yang diperlukan untuk membuat perangkat tambahan di bagian depan akan merusak transistor yang ada di bawahnya.

Para peneliti MIT mengatasi masalah ini dan mengembangkan teknik integrasi untuk menumpuk komponen aktif di bagian belakang chip.

“Jika kita dapat menggunakan platform back-end ini untuk menambahkan lapisan aktif transistor, tidak hanya interkoneksi, hal ini akan membuat kepadatan integrasi chip jauh lebih tinggi dan meningkatkan efisiensi energinya,” jelas Shao.

Para peneliti mencapai hal ini dengan menggunakan bahan baru, indium oksida amorf, sebagai lapisan saluran aktif transistor back-end mereka. Lapisan saluran aktif adalah tempat fungsi penting transistor berlangsung.

Karena sifat unik dari indium oksida, mereka dapat “menumbuhkan” lapisan yang sangat tipis dari bahan ini pada suhu hanya sekitar 150 derajat Celcius di bagian belakang sirkuit yang ada tanpa merusak perangkat di bagian depan.

Menyempurnakan prosesnya

Mereka dengan hati-hati mengoptimalkan proses fabrikasi, yang meminimalkan jumlah cacat pada lapisan bahan indium oksida yang tebalnya hanya sekitar 2 nanometer.

Beberapa cacat, yang dikenal sebagai kekosongan oksigen, diperlukan agar transistor dapat menyala, tetapi jika terlalu banyak cacat maka transistor tidak akan berfungsi dengan baik. Proses fabrikasi yang dioptimalkan ini memungkinkan para peneliti untuk menghasilkan transistor yang sangat kecil yang beroperasi dengan cepat dan bersih, menghilangkan banyak energi tambahan yang diperlukan untuk mematikan dan menghidupkan transistor.

Berdasarkan pendekatan ini, mereka juga membuat transistor back-end dengan memori terintegrasi yang hanya berukuran sekitar 20 nanometer. Untuk melakukan ini, mereka menambahkan lapisan bahan yang disebut feroelektrik hafnium-zirkonium-oksida sebagai komponen memori.

Transistor memori kompak ini menunjukkan kecepatan peralihan hanya 10 nanodetik, mencapai batas instrumen pengukuran tim. Peralihan ini juga memerlukan tegangan yang jauh lebih rendah dibandingkan perangkat serupa, sehingga mengurangi konsumsi listrik.

Dan karena transistor memori sangat kecil, para peneliti dapat menggunakannya sebagai platform untuk mempelajari fisika dasar dari masing-masing unit feroelektrik hafnium-zirkonium-oksida.

“Jika kita bisa lebih memahami fisika, kita bisa menggunakan bahan ini untuk banyak aplikasi baru. Energi yang digunakan sangat minim, dan ini memberi kita banyak fleksibilitas dalam merancang perangkat. Ini benar-benar bisa membuka banyak jalan baru untuk masa depan,” kata Shao.

Para peneliti juga bekerja sama dengan tim di Universitas Waterloo untuk mengembangkan model kinerja transistor back-end, yang merupakan langkah penting sebelum perangkat tersebut dapat diintegrasikan ke dalam sirkuit dan sistem elektronik yang lebih besar.

Di masa depan, mereka ingin mengembangkan demonstrasi ini dengan mengintegrasikan transistor memori back-end ke dalam satu sirkuit. Mereka juga ingin meningkatkan kinerja transistor dan mempelajari cara mengontrol sifat feroelektrik hafnium-zirkonium-oksida dengan lebih baik.

“Sekarang, kami dapat membangun platform elektronik serbaguna di bagian belakang sebuah chip yang memungkinkan kami mencapai efisiensi energi tinggi dan berbagai fungsi berbeda dalam perangkat yang sangat kecil. Kami memiliki arsitektur dan material perangkat yang bagus untuk digunakan, namun kami perlu terus berinovasi untuk mengungkap batas kinerja tertinggi,” kata Shao.

Pekerjaan ini sebagian didukung oleh Semiconductor Research Corporation (SRC) dan Intel. Fabrikasi dilakukan di Laboratorium Teknologi Mikrosistem MIT dan fasilitas MIT.nano.